# **TETHRA: TDM OVER ETHERNET ROUTER AND ANALYZER**

### Mihai Fagadar-Cosma, Liviu D. Faniciu and Mihai V. Micea\*

Department of Computer Science and Engineering (DCSE), "Politehnica" University of Timisoara,

2, Vasile Parvan Bv., 300223 – Timişoara, Romania \* micha@dsplabs.cs.utt.ro

**Abstract:** This paper focuses on the design and implementation of a digital equipment capable of acting as a bridge between two different networks: a plesiochronous digital hierarchy and a Fast-Ethernet network. The device, named TETHRA (TDM over Ethernet Router and Analyzer), is capable of performing the basic functions of a router, by transmitting the data contained in the received time-division multiplex (TDM) frames towards equipments connected to the Ethernet network, and vice-versa, in a transparent manner.

Key words: PCM E1, TDM over Ethernet, transparent data routing, protocol analysis

# **INTRODUCTION**

The TETHRA system represents a digital equipment able to connect two different networks: a plesiochronous digital hierarchy (PDH) [Cou01] based on E1 pulse code modulation (PCM) frames [ITU98] and a Fast-Ethernet network [IEE02]. The features provided by this device include:

- management and configuration of the data routes, for individual time-slots (TSs) and for userdefined groups of TSs, via commands received through the Ethernet interface;

- routing capabilities for data contained in the TSs of the incoming PCM E1 frames towards the Ethernet network, based on predefined data routes;

- abilities to receive data from equipments located in the Ethernet network and insert it into the TSs of the outgoing PCM frames;

- mixing of PCM TSs: data transported by a time-slot (TS) of an incoming PCM frame can be inserted into a TS of an outgoing PCM frame, based on the defined data routes;

- abilities to change data routes dynamically, without shutting-down or restarting the PCM interfaces; the user can also specify the number of received PCM frames after which the data will be transmitted into the Ethernet network.

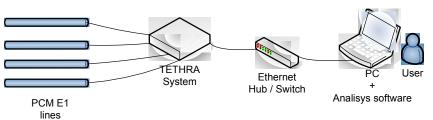

The equipment operates at the data-link level of the network [ISO94], thus offering the best performance with respect to the response time and network usage. The capabilities of the TETHRA system make it ideal for a wide range of applications from the telecommunications domain, such as remote protocol analyzers, as shown in Figure 1.

Figure 1. TETHRA system used as a remote protocol analyzer

On one side, the system is connected to the PCM lines, and on the other to a PC running the analysis software, via an Ethernet connection. The responsibility of the analysis software is to configure the data routes of the system, so that the desired TSs will be routed towards the PC, analyze the received data and display the results. The analysis software can even change the contents of the PCM TSs and then send them back to the PCM line, a feature like this being extremely useful for diagnostic purposes, as in the case of Signaling System #7 protocol [Cou01].

# **TETHRA SYSTEM IMPLEMENTATION**

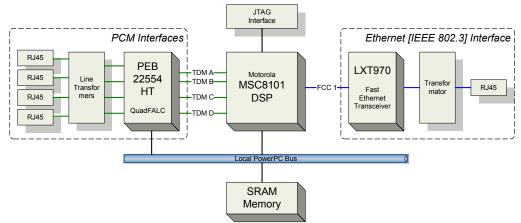

The TETHRA system was implemented using the Freescale MSC8101 Application Development System (MSC8101ADS) [Mot01], which represents a very good platform for our purposes, due to its advanced connectivity options, as shown in Figure 2.

Figure 2. TETHRA system implementation with the MSC8101ADS

The four PCM interfaces provide the means for connecting to E1/T1/J1 lines, while the Full-Duplex Fast-Ethernet interface supports the communication with the Ethernet network. The MSC8101 "Network Ready" digital signal processor (DSP) represents the core of the system, its Communications Processor Module (CPM) and large on-chip SRAM memory providing an ideal architecture for this type of applications.

With the MSC8101ADS as the hardware platform, the system's software was build using the Metrowerks CodeWarrior for StarCore IDE, version 2.0. The software runs directly on the MSC8101 DSP, without any underlying operating system (OS), and integrates the PCM and Ethernet communication drivers and the data routing management part. The architecture of the MSC8101 CPM allowed us to reduce data relocation operations so that the system can ensure minimum delays when routing information between the two networks.

The system was tested in the *DSPLabs* laboratory, using loop-back modes for the four PCM interfaces, as the architecture of the MSC8101ADS board, due to the presence of an ATM transceiver, allowed only one external E1 line to be connected when the Fast-Ethernet interface is being used. Some operating parameters of the system, like the number of received TDM frames after which data is being routed and the number of data routes, can be changed interactively, so that the network load and response time can be measured under various operating conditions. Some of the most interesting results are displayed in Table 1.

| Network type    | Ethernet Full–Duplex<br>(20 Mbps) |     |     | Fast Ethernet (100 Mbps) |     |     | Fast Ethernet Full–<br>Duplex (200 Mbps) |     |     |

|-----------------|-----------------------------------|-----|-----|--------------------------|-----|-----|------------------------------------------|-----|-----|

| #Frames<br>#MAC | 8                                 | 16  | 32  | 8                        | 16  | 32  | 8                                        | 16  | 32  |

| 16              | _                                 | 95% | 87% | 22%                      | 19% | 17% | 11%                                      | 10% | 9%  |

| 32              | _                                 | _   | 92% | 32%                      | 21% | 18% | 16%                                      | 11% | 10% |

| 64              | _                                 | _   | _   | 64%                      | 32% | 20% | 32%                                      | 16% | 10% |

| 128             | _                                 | _   | _   | _                        | 64% | 32% | 64%                                      | 32% | 16% |

Table 1. Network load caused by TETHRA system under various operating conditions

#### **DISCUSSION OF THE RESULTS**

The TETHRA system supports up to 128 voice channels in full-duplex mode, each one with a data rate of 8 kbps. The experimental results shown in Error: Reference source not found take into consideration the case in which a channel is routed towards a single Medium Access Control (MAC) address [IEE02]. The *#Frames* parameter indicates the number of received TDM frames after which data routing takes place, while the *#MAC* parameter indicates the number of different MAC addresses to which data will be routed (e.g. for *#MAC=16*, each MAC address will receive and transmit data from/to 8 channels). If multiple channels are routed towards a MAC address, a single Ethernet frame will be sent to that address, containing the data collected from all the channels, over *#Frames* TDM frames.

The delay introduced by the TETHRA system is equal to the value of *#Frames* divided by 8, expressed in milliseconds. Since the minimum value of *#Frames* is 8, the minimum delay will be of 1 ms, and will remain constant as long as *#Frames* is not changed. This offers faster response time than other similar solutions like TDMoIP [Ste00].

Based on the results in Table 1, we conclude that the network load decreases when #MAC decreases and #Frames increases, due to the fact that less Ethernet frames are sent over the network. In normal operating conditions, when, for example, TETHRA acts as a part of a protocol analyzer,

multiple channels are routed towards a single MAC address, which will result in a lower network load, especially on Fast-Ethernet networks.

### CONCLUSION

A new equipment, TETHRA, capable of transporting data between PDH and Ethernet networks, was designed and implemented using the MSC8101ADS platform. The routing capabilities of this system enable Ethernet-based devices to communicate with digital equipments that use PCM frames, in particular over E1 communication lines.

The efficient routing mechanisms implemented into this device recommend it for designing remote protocol analyzers, or other equipments such as Base Station Subsystem (BSS) emulators for GSM networks [Hei99].

#### REFERENCES

- [Cou01] Couch W. L., 2001, "Digital and Analog Communication Systems", 6<sup>th</sup> Edition, Prentice Hall, New York.

- [ITU98] ITU, 1998, "Synchronous Frame Structures Used at 1544, 6312, 2048, 8448 and 44736 Kbit/s Hierarchical Levels", Geneva, ITU-T Std. G.704.

- [IEE02] IEEE Computer Society, 2002, "Carrier Sense Multiple Access with Collision Detection (CSMA/CD) Access Method and Physical Layer Specifications", New York, Std. 802.3.

- [ISO94] ISO, 1994, "Information Technology Open Systems Interconnection Basic Reference Model : The Basic Model", Geneva, ISO/IEC Std. 7498-1.

- [Ste00] Stein Y., Schwartz E., 2000, "Ever thought about extending circuits over IP?", *Telecom. Mag.*, No. 11, pp. (89-94).

- [Hei99] Heine G., 1999, "GSM Networks: Protocols, Terminology and Implementation", Artech House, Norwood.

- [Mot01] Motorola Semiconductor, 2001, "MSC8101ADS User's Manual", Rev. 1.0, Israel.